- 您现在的位置:买卖IC网 > Sheet目录2098 > MK2069-04GILFTR (IDT, Integrated Device Technology Inc)IC VCXO CLK TRANSLATOR 56-TSSOP

MK2069-04

VCXO-BASED UNIVERSAL CLOCK TRANSLATOR

VCXO AND SYNTHESIZER

IDT VCXO-BASED UNIVERSAL CLOCK TRANSLATOR

3

MK2069-04

REV J 051310

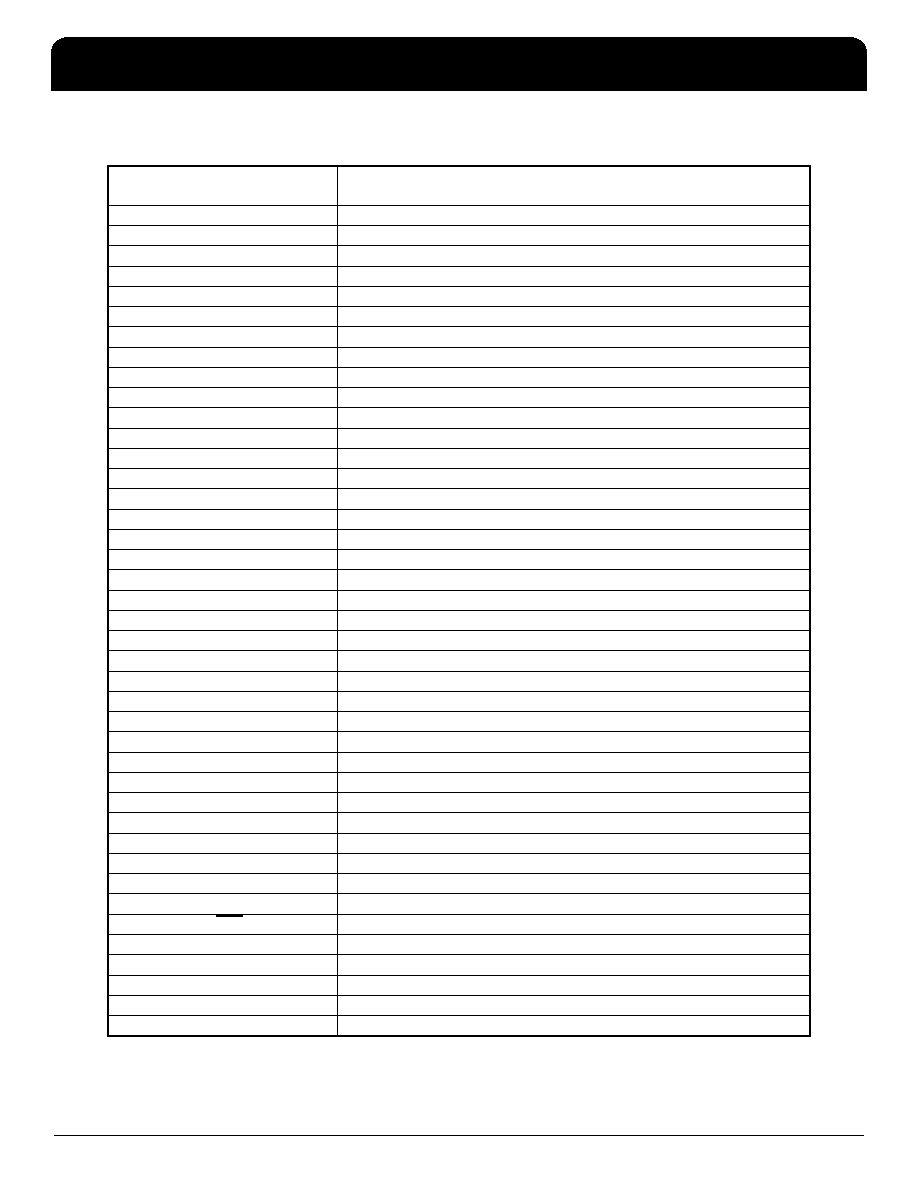

Pin Descriptions

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

RV5

Input

Reference Divider bit 5 input, VCXO PLL, internal pull-up.

2

RV6

Input

Reference Divider bit 6 input, VCXO PLL, internal pull-up.

3

RV7

Input

Reference Divider bit 7 input, VCXO PLL, internal pull-up.

4

RV8

Input

Reference Divider bit 8 input, VCXO PLL, internal pull-up.

5

FT0

Input

Feedback Divider bit 0 input, Translator PLL, internal pull-up.

6

FT1

Input

Feedback Divider bit 1 input, Translator PLL, internal pull-up.

7

FT2

Input

Feedback Divider bit 2 input, Translator PLL, internal pull-up.

8

RV9

Input

Reference Divider bit 9, VCXO PLL, internal pull-up.

9

RV10

Input

Reference Divider bit 10, VCXO PLL, internal pull-up.

10

RV11

Input

Reference Divider bit 11, VCXO PLL, internal pull-up.

11

ST

Input

Scaling Divider selection bit, Translator PLL, internal pull-up.

12

VDDT

Power

Power Supply connection for translator PLL.

13

GNDT

Ground

Ground connection for translator PLL.

14

X1

—

Crystal oscillator input. Connect this pin to the external quartz crystal.

15

VDDV

Power

Power Supply connection for VCXO PLL.

16

X2

—

Crystal oscillator output. Connect this pin to the external quartz crystal.

17

GNDV

Ground

Ground connection for VCXO PLL.

18

LFR

—

Loop filter connection, reference node. Refer to loop filter circuit on page 6.

19

LF

—

Loop filter connection, active node. Refer to loop filter circuit on page 6.

20

ISET

—

Charge pump current setting pin. Refer to loop filter circuit on page 6.

21

FV0

Input

Feedback Divider bit 0 input, VCXO PLL, internal pull-up.

22

FV1

Input

Feedback Divider bit 1input, VCXO PLL, internal pull-up.

23

FV2

Input

Feedback Divider bit 2 input, VCXO PLL, internal pull-up.

24

FV3

Input

Feedback Divider bit 3 input, VCXO PLL, internal pull-up.

25

FV4

Input

Feedback Divider bit 4 input, VCXO PLL, internal pull-up.

26

FV5

Input

Feedback Divider bit 5 input, VCXO PLL, internal pull-up.

27

FV6

Input

Feedback Divider bit 6 input, VCXO PLL, internal pull-up.

28

FV7

Input

Feedback Divider bit 7 input, VCXO PLL, internal pull-up.

29

FV8

Input

Feedback Divider bit 8 input, VCXO PLL, internal pull-up.

30

FV9

Input

Feedback Divider bit 9 input, VCXO PLL, internal pull-up.

31

FV10

Input

Feedback Divider bit 10 input, VCXO PLL, internal pull-up.

32

FV11

Input

Feedback Divider bit 11 input, VCXO PLL, internal pull-up.

33

RV0

Input

Reference Divider bit 0, VCXO PLL, internal pull-up.

34

RV1

Input

Reference Divider bit 1, VCXO PLL, internal pull-up.

35

ICLK

Input

Reference clock input, 5 V tolerant input

36

CLR

Input

Clear input, allows VCXO to free-run when low, internal pull-up.

37

LDC

—

Lock detector threshold setting circuit connection. Refer to circuit on page 10.

38

GND

Ground

Ground connection for internal digital circuitry.

39

LDR

Power

Lock detector threshold setting circuit connection. Refer to circuit on page 10.

40

RCLK

—

VCXO PLL phase detector Reference Clock output.

41

GNDP

Ground

Ground connection for output drivers (VCLK, TCLK, RCLK, LD, LDR).

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MK2302S-01LFTR

IC MULTIPLIER/ZD BUFFER 8-SOIC

MK2304S-2LF

IC PLL ZD BUFFER LO SKEW 8-SOIC

MK2703SILF

IC PLL AUD CLK SYNTHESIZER 8SOIC

MK2704SLF

IC PLL AUD CLK SYNTHESIZER 8SOIC

MK2716SLFTR

IC CLK SYNTHESIZER HDTV 8-SOIC

MK2732-06GLF

IC VCXO/MULTIPLIER 16-TSSOP

MK2745-21SLFTR

IC CLK SOURCE DVD/MPEG 16-SOIC

MK2745-24SLF

IC CLK SOURCE DVD/MPEG 16-SOIC

相关代理商/技术参数

MK2069-04GITR

功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

MK206N 454634/1/MK

制造商:NSF (CONTROLS) 功能描述:WAFER MK 2POLE 6 POS 制造商:NSF (CONTROLS) 功能描述:WAFER, MK, 2POLE, 6 POS 制造商:NSF (CONTROLS) 功能描述:WAFER, MK, 2POLE, 6 POS; For Use With:Rotary Switches; No. of Poles:2; No. of Positions:6; SVHC:No SVHC (19-Dec-2012); Contact Current @ Contact Voltage AC Max:500mA; Contact Current AC Max:5A; Contact Current DC Max:5A; Contact ;RoHS Compliant: Yes

MK206S 454634MK

制造商:NSF (CONTROLS) 功能描述:WAFER MK 2POLE 6 POS 制造商:NSF (CONTROLS) 功能描述:WAFER, MK, 2POLE, 6 POS 制造商:NSF (CONTROLS) 功能描述:WAFER, MK, 2POLE, 6 POS; No. of Poles:2; No. of Positions:6; SVHC:No SVHC (19-Dec-2012); Contact Current @ Contact Voltage AC Max:500mA; Contact Current AC Max:5A; Contact Current DC Max:5A; Contact Current Rating:5A; Contact ;RoHS Compliant: Yes

MK20-B-100W

功能描述:近程传感器 1 Form A Cylindrical Term.

RoHS:否 制造商:Vishay Semiconductors 感应方式:Optical 感应距离:1 mm to 200 mm 电源电压:2.5 V to 3.6 V 安装风格:SMD/SMT 输出配置:Digital 最大工作温度:+ 85 C 最小工作温度:- 25 C 系列:VCNL3020

MK20-B-100W_DE

制造商:MEDER 制造商全称:Meder Electronic 功能描述:(deutsch) MK Reed Sensor

MK20-B-500W

制造商:MEDER 制造商全称:Meder Electronic 功能描述:MK Reed Sensor

MK20-B-500W_DE

制造商:MEDER 制造商全称:Meder Electronic 功能描述:(deutsch) MK Reed Sensor

MK20-C-100W

制造商:Willow Technologies 功能描述:MICRO REED SENSOR